Graduate Theses and Dissertations

Graduate School

11-19-2015

# Optical Communication Using Hybrid Micro Electro Mechanical Structures (MEMS) and Commercial Corner Cube Retroreflector (CCR)

Sunny Kedia *University of South Florida*, skedia@mail.usf.edu

Follow this and additional works at: http://scholarcommons.usf.edu/etd

Part of the <u>Electrical and Computer Engineering Commons</u>, <u>Nanoscience and Nanotechnology</u> Commons, and the Optics Commons

# Scholar Commons Citation

Kedia, Sunny, "Optical Communication Using Hybrid Micro Electro Mechanical Structures (MEMS) and Commercial Corner Cube Retroreflector (CCR)" (2015). *Graduate Theses and Dissertations*. http://scholarcommons.usf.edu/etd/5969

This Dissertation is brought to you for free and open access by the Graduate School at Scholar Commons. It has been accepted for inclusion in Graduate Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact scholarcommons@usf.edu.

# Optical Communication Using Hybrid Micro Electro Mechanical Structures (MEMS) and Commercial Corner Cube Retroreflector (CCR)

by

Sunny Kedia

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Department of Electrical Engineering

College of Engineering

University of South Florida

Co-Major Professor: Sanjukta Bhanja, Ph.D. Co-Major Professor: Scott Samson, Ph.D. Shekhar Bhansali, Ph.D. Paris Wiley, Ph.D. Wilfred Moreno, Ph.D.

Date of Approval: October 27, 2015

Keywords: evanescent waves, electrostatic actuators, unattended sensors, scattering microstructures, Michelson interferometry

Copyright © 2015, Sunny Kedia

# **DEDICATION**

To my loving son, wife, parents and other family members who inspired me and stood by me to help me finish. I would like to dedicate my work to their sacrifice and support.

#### **ACKNOWLEDGMENTS**

The path to complete a doctoral research thesis is lengthy and grueling. During this journey of my dissertation, Dr. Scott Samson encouraged me, mentored me, and stood by me at each step. Without his advice and zeal for the technology, this research probably would not have happened. Scott has guided me, worked with me as a colleague, and provided candid opinion as a friend. This unwavering support means everything to me, and I don't think I can thank him enough for this.

I would also like to express gratitude to Dr. Shekhar Bhansali for mentoring, inspiring, and providing a path for me to complete my dissertation. Thanks to Dr. Sanjukta Bhanja for accepting me as her student and working along with Shekhar and Scott in letting me complete my dissertation. Also, I would like to recognize efforts of Dr. Wilfrido Moreno and Dr. Paris Wiley for being a part of my dissertation team.

Special credits go to the staff of SRI International to provide infrastructure and provision to complete my dissertation, especially Dr. Chris Lantman and Jeanie Graham. I would also like to acknowledge my fellow researchers Dr. Shinzo Onishi, Dr. Weidong Wang, Lawrence Bach, Ben Rossie, William Chu, and Dr. Brian Slovick for their timely help and cooperation.

Finally, this dissertation would not have been possible without the support of my son Reyansh, wife Ritika, mother Chanda, father Subhash, other family members and friends who supported me in their own way.

# TABLE OF CONTENTS

| LIST OF T | ABLES                                                              | iv |

|-----------|--------------------------------------------------------------------|----|

| LIST OF F | IGURES                                                             | V  |

| ABSTRAC   | T                                                                  | ix |

| CHAPTER   | 1: INTRODUCTION                                                    | 1  |

|           | Objective and Background                                           |    |

|           | 1.1.1 Corner Cube Retroreflector (CCR)                             | 3  |

|           | 1.1.2 Hollow CCR                                                   |    |

|           | 1.1.3 Total Internal Reflection (TIR) CCR                          | 4  |

| 1.2       | Literature Review                                                  | 5  |

| 1.3       | Previous Work at USF                                               | 9  |

| 1.4       | Organization of the Dissertation                                   | 11 |

| CHAPTER   | 2: DESIGN AND CALCULATIONS OF OPTICAL, MEMS CHIP AND               | 1/ |

| 0.1       | SYSTEM PARAMETERS                                                  |    |

| 2.1       | Factors Impacting Range in a CCR Based Communication System        |    |

|           | 2.1.1 Orthogonality of the Mirrors                                 |    |

|           | 2.1.2 Flatness of the Mirrors                                      |    |

| 2.2       | CCR MEMS Hybrid Concept                                            |    |

| 2.2       | 2.2.1 Principle of TIR and Evanescent Wave Coupling                |    |

|           | 2.2.2 Determination of Penetration Depth for Different Wavelengths |    |

|           | 2.2.3 Incidence Angle                                              |    |

|           | 2.2.4 Selection of Commercial CCR                                  |    |

| 23        | Requirements for the Receiver Unit                                 |    |

|           | Requirements of the MEMS Chip                                      |    |

| 2.1       | 2.4.1 MEMS Electrostatic Structures                                |    |

|           | 2.4.2 Calculation of Energy Needed Per Bit                         |    |

| 2.5       | System Parameter                                                   |    |

|           | Conclusion.                                                        |    |

| 0         |                                                                    |    |

| CHAPTER   | 3: DESIGN AND FABRICATION OF THE MEMS CHIP                         | 34 |

|           | Development of the Process                                         |    |

|           | Design of Structures and Electrodes                                |    |

|           | 3.2.1 Silicon on Insulator (SOI)                                   |    |

|           | 3.2.2 Glass Wafer                                                  |    |

| 3.3     | Fabrication of MEMS Chip                            | 44  |

|---------|-----------------------------------------------------|-----|

|         | 3.3.1 Silicon on Insulator (SOI) Wafer              | 45  |

|         | 3.3.1.1 Structure                                   | 45  |

|         | 3.3.1.2 Structure Metal                             | 51  |

|         | 3.3.2 Release of SOI Chips                          | 55  |

|         | 3.3.3 Glass Wafer                                   |     |

|         | 3.3.3.1 Indent                                      | 57  |

|         | 3.3.3.2 Indium Tin Oxide (ITO)                      | 58  |

|         | 3.3.3.3 ITO Metal                                   | 61  |

| CHAPTER | 4: PACKAGING OF THE MEMS CHIP AND TESTING OF THE    |     |

|         | COMMUNICATION SYSTEM                                | 63  |

| 4.1     | Testing of MEMS Structures on SOI Chip              | 63  |

|         | 4.1.1 Testing Structures                            |     |

|         | 4.1.2 Testing Array                                 | 71  |

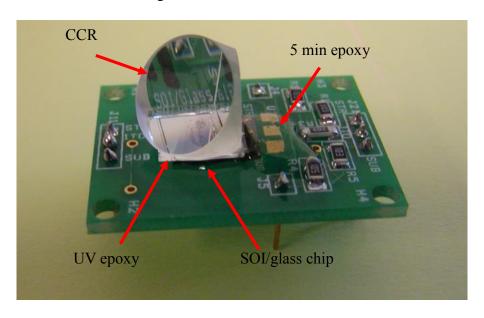

| 4.2     | Bonding of the SOI Glass Chip                       | 74  |

| 4.3     | PCB Mounting of MEMS Chip                           | 75  |

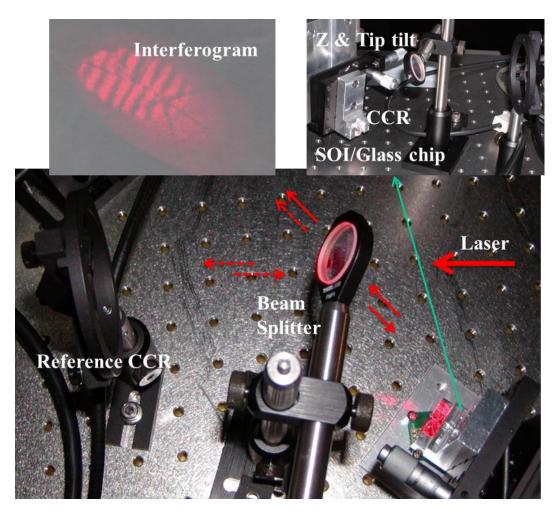

| 4.4     | Michelson Interferometry                            | 76  |

|         | 4.4.1 Mechanical Stages                             | 77  |

|         | 4.4.2 Dispensing Experiment                         | 79  |

|         | 4.4.3 Optical Set Up                                | 81  |

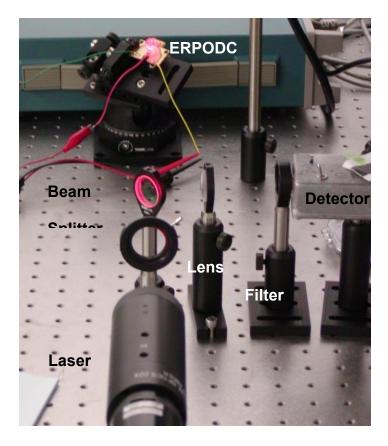

| 4.5     | Bench Top CCR Modulation Testing                    | 83  |

| CHAPTER | 5: DEVELOPMENT OF TRANSMITTER AND RECEIVER UNIT AND |     |

|         | IMPROVEMENT IN MEMS STRUCTURES                      | 86  |

| 5.1     | Development of Transmitter Unit                     | 86  |

|         | Receiver Prototype Unit                             |     |

|         | Testing Optical Communication                       |     |

|         | 5.3.1 Precision Bonding Conformation                |     |

|         | 5.3.2 Phase Shift Keying (PSK)                      | 92  |

|         | 5.3.3 Long Range Communication                      |     |

| 5.4     | Improvements in MEMS Structures                     | 94  |

|         | 5.4.1 Mechanical Abrasion                           | 95  |

|         | 5.4.2 Multiple Exposures of the Photomask           | 96  |

|         | 5.4.3 Plasma Dry Etching                            | 97  |

|         | 5.4.4 Wet Etching                                   | 99  |

|         | 5.4.4.1 Isotropic Etching                           | 99  |

|         | 5.4.4.2 Anisotropic Etching                         | 100 |

|         | 5.4.5 Using Polysilicon on an Insulator Wafer       | 102 |

| 5.5     | Improvements in the Receiver Unit                   | 104 |

| CHAPTER | 6: CONCLUSION AND FUTURE WORK                       | 107 |

|         |                                                     |     |

| 0.1     | Conclusion                                          | 107 |

| REFERENCES                       | 111      |

|----------------------------------|----------|

| APPENDIX A: COPYRIGHT PERMISSION | 116      |

| ABOUT THE AUTHOR                 | END PAGE |

# LIST OF TABLES

| Table 2-1: Beam spot at the receiver after beam divergence 0.5mrad (100 arc second) and misalignment 30 arc second (0.15 mrad) due to CCR at different ranges |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 2-2: Variation of MEMS structures along with their calculated pull-in voltages and resonance frequency                                                  |     |

| Table 3-1: DRIE Bosch process details                                                                                                                         | 47  |

| Table 3-2: RIE process parameters                                                                                                                             | 48  |

| Table 3-3: ITO film conductivity with various processing parameters                                                                                           | 59  |

| Table 4-1: Pull-in voltage measured for various MEMS plate and spring styles compared to calculated pull in voltage from table 2-2                            | 71  |

| Table 5-1: Summary of optical reflectivity from mechanical and plasma processed samples of silicon and polysilicon-coated silicon                             | 98  |

| Table 5-2: Summary of optical reflectivity from wet processed samples of silicon and polysilicon                                                              | 101 |

# LIST OF FIGURES

| Figure 1-1: Hollow CCR                                                                                                | 3  |

|-----------------------------------------------------------------------------------------------------------------------|----|

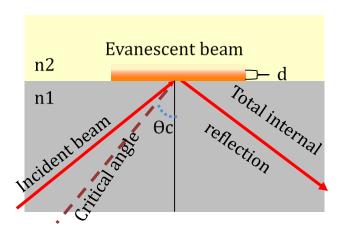

| Figure 1-2: Total internal reflection CCR                                                                             | 5  |

| Figure 1-3: Automated assembled MEMS CCR [17]                                                                         | 6  |

| Figure 1-4: Hollow CCR fabricated with 250-µm-long vertical mirror and movable horizontal mirror [32, 33]             | 10 |

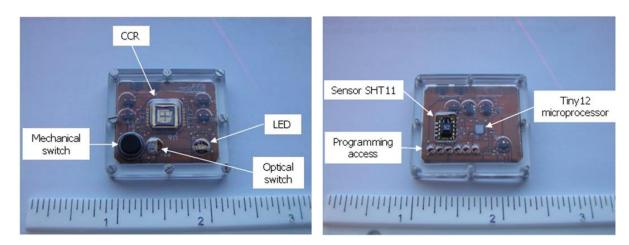

| Figure 1-5: Front and back side of a packaged MEMS CCR with temperature sensor [36]                                   | 11 |

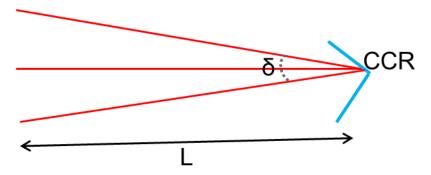

| Figure 2-1: CCR mirror misalignment causing the retroreflected signal to disperse at long ranges                      | 13 |

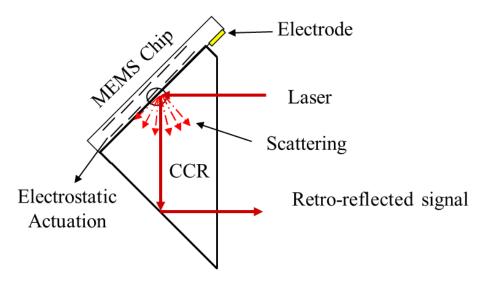

| Figure 2-2: Commercial CCR and MEMS chip concept                                                                      | 15 |

| Figure 2-3: Total internal reflection occurs when the incident angle is greater than the critical angle.              | 16 |

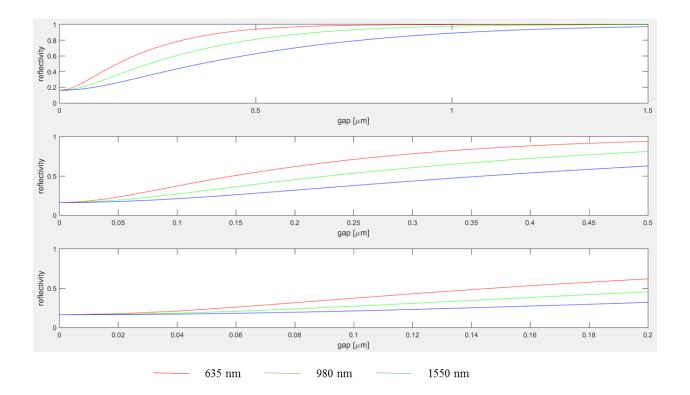

| Figure 2-4: Reflectivity at different wavelengths illustrating how reflected beam penetration depth changes with gap. | 18 |

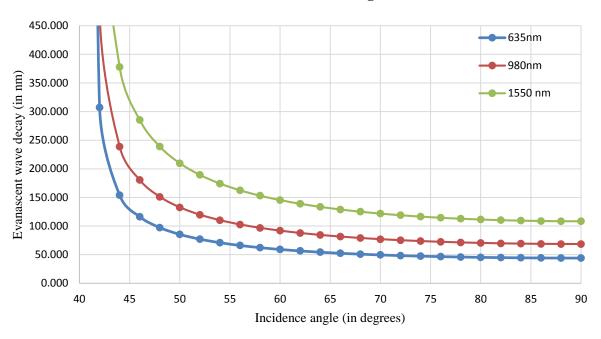

| Figure 2-5: Evanescent wave decay vs incidence angle of different wavelengths with 41.35° as critical angle           | 20 |

| Figure 2-6: Acceptance angle of TIR-based CCR vs. its refractive index                                                | 21 |

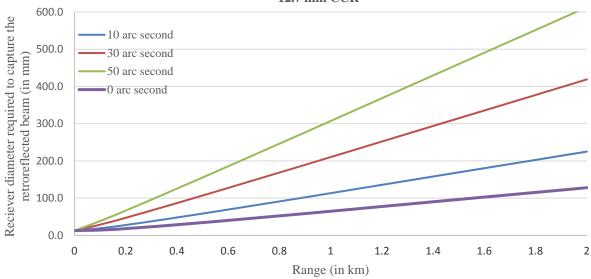

| Figure 2-7: Receiver size required vs communication range at different misalignment angles                            | 24 |

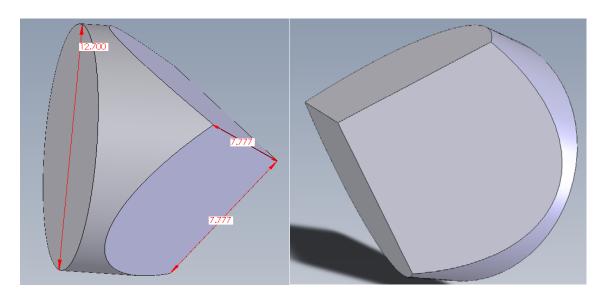

| Figure 2-8: 3D model of the CCR illustrating the height and other dimensions [12]                                     | 25 |

| Figure 2-9: An electrostatic actuator schematic with a spring connected to one of the parallel plates of capacitor.   | 26 |

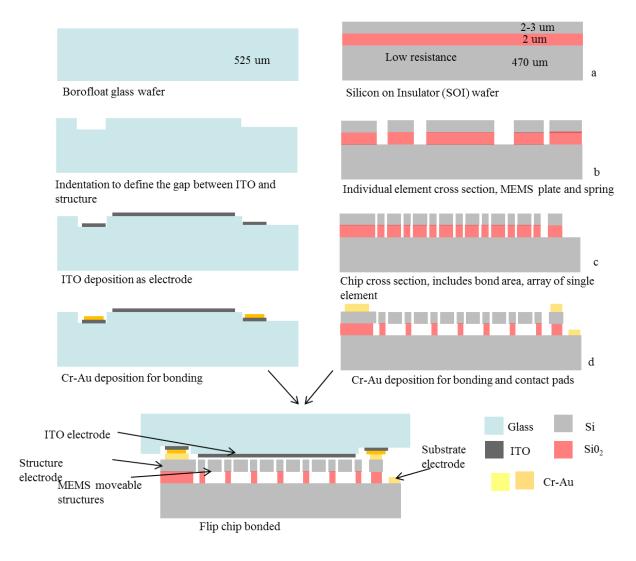

| Figure 3-1: Cross section view of the glass and SOI wafer.                                                            | 36 |

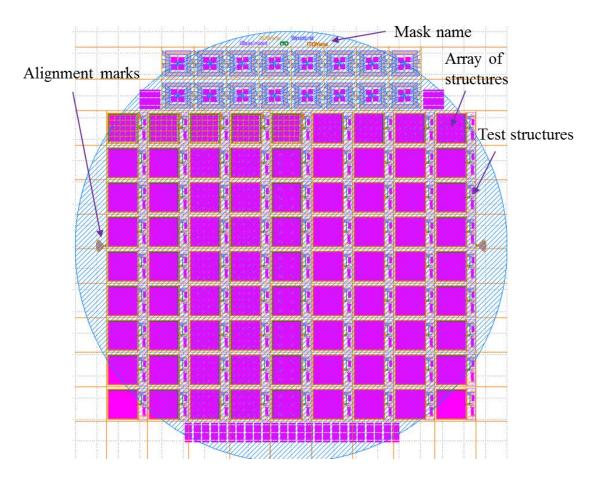

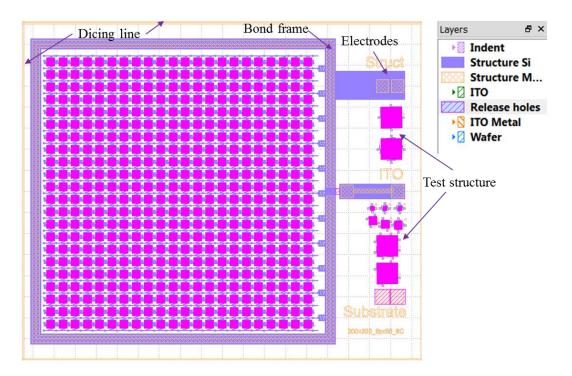

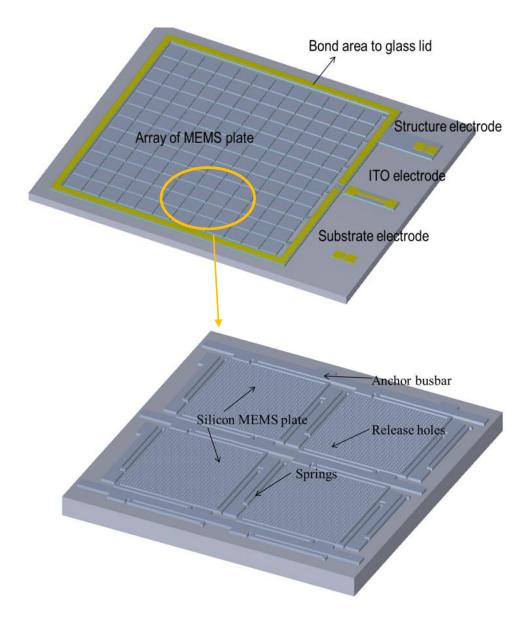

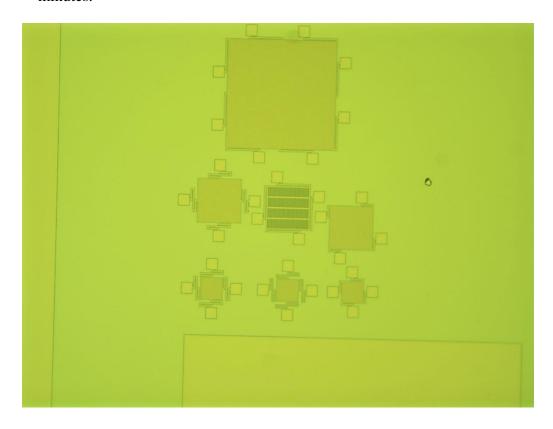

| Figure 3-2: Overall view of both SOI and glass mask design                                                            | 38 |

| Figure 3-3: | 200 x 200 μm MEMS plate array with layers                                                                                                                        | 39 |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

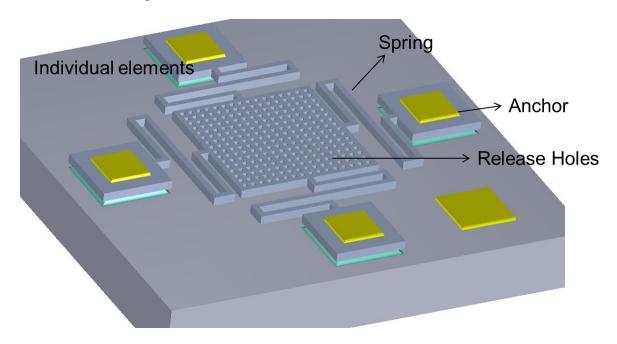

| Figure 3-4: | Top is a 3D solid model developed in SoftMEMS illustrating the electrodes and MEMS array.                                                                        | 40 |

| Figure 3-5: | 3D rendering of a 100 x 100 $\mu m$ MEMS plate after release illustrating that the oxide (green) is removed under MEMS plate and springs but not the anchor area | 42 |

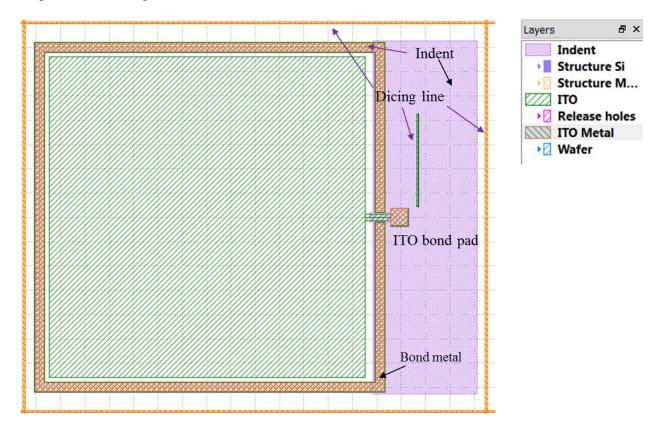

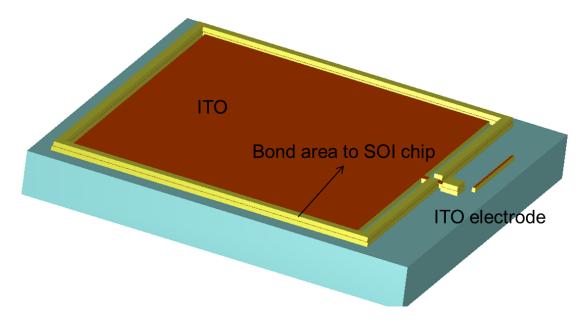

| Figure 3-6: | 2D image of a glass lid                                                                                                                                          | 43 |

| Figure 3-7: | Glass chip design for bonding a conductive glass lid within a few nm of the MEMS SOI chip                                                                        | 44 |

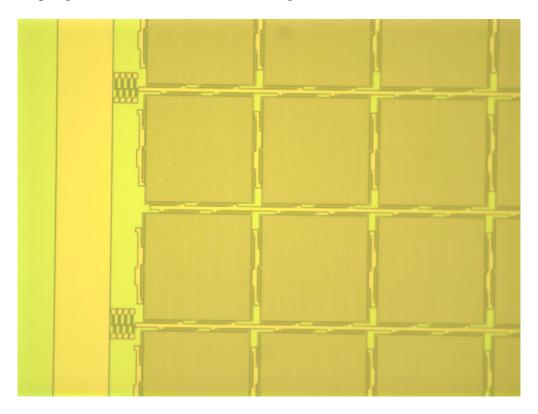

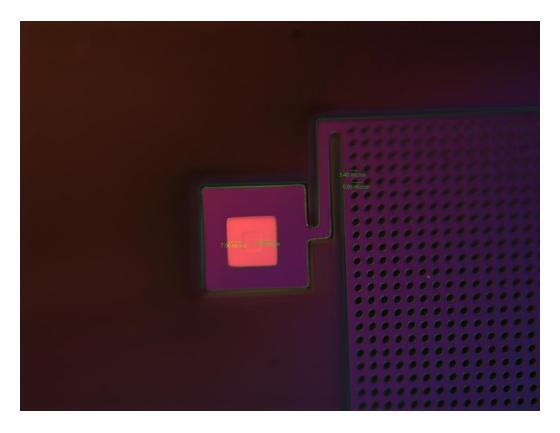

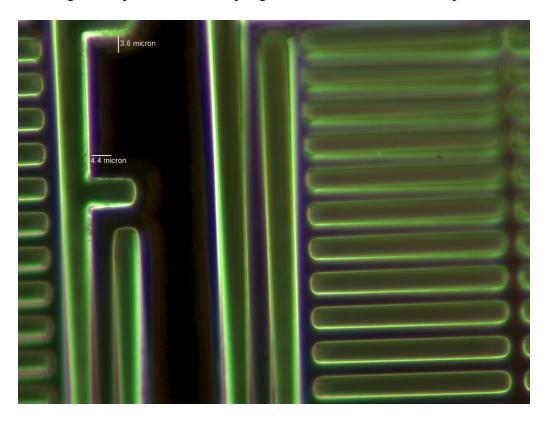

| Figure 3-8: | Microscope optical image after lithography and development of the resist and patterning <i>structure</i> mask                                                    | 46 |

| Figure 3-9: | Microscope image after DRIE and RIE                                                                                                                              | 49 |

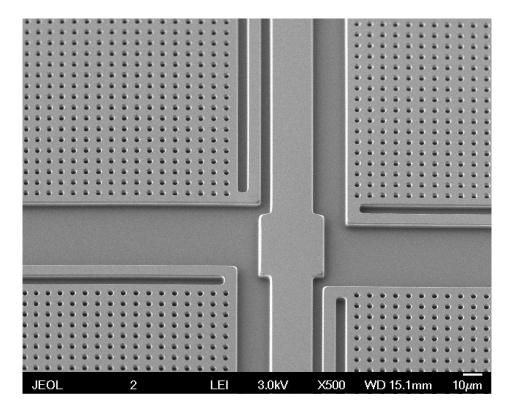

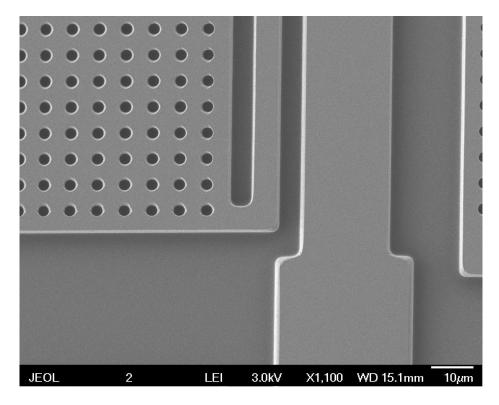

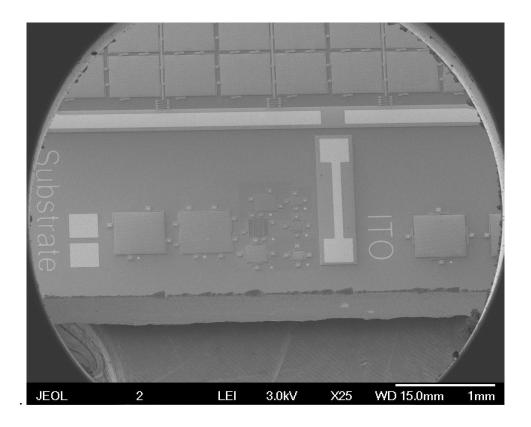

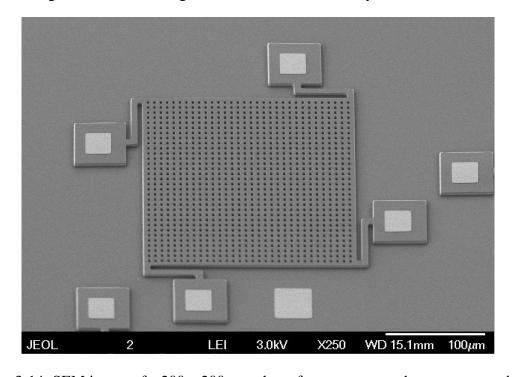

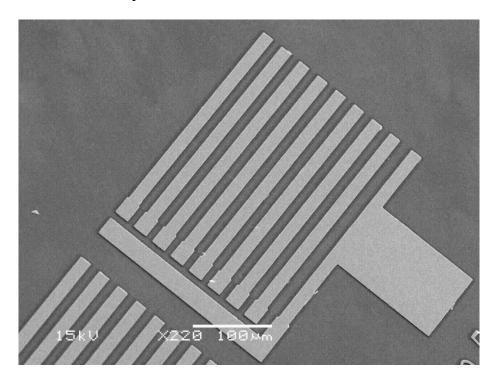

| Figure 3-10 | Examing electron microscope (SEM) image illustrating a 2x2 array area                                                                                            | 50 |

| Figure 3-11 | : Zoomed-in SEM image illustrating the busbar connecting the mirrors and release hole and spring area                                                            | 50 |

| Figure 3-12 | 2: Undercut in chrome films after etching for 75 sec, with undercut of 7 µm                                                                                      | 52 |

| Figure 3-13 | S: SEM image of test area and initial array of the structures                                                                                                    | 54 |

| Figure 3-14 | SEM image of a 200 x 200 μm plate after structure and structure metal mask                                                                                       | 54 |

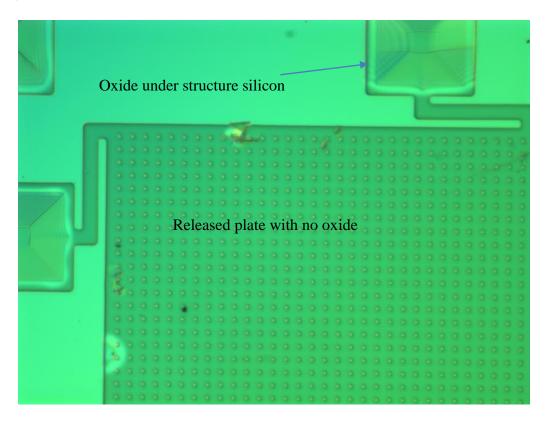

| Figure 3-15 | E: Microscope image illustrating oxide in bond pad area and no oxide under the MEMS plate area after 75 second of release in 49% hydro fluoric acid              | 55 |

| Figure 3-16 | 5: Undercut of silicon oxide (~4 μm)                                                                                                                             | 56 |

| Figure 3-17 | : Post-annealing features of ITO after liftoff process                                                                                                           | 60 |

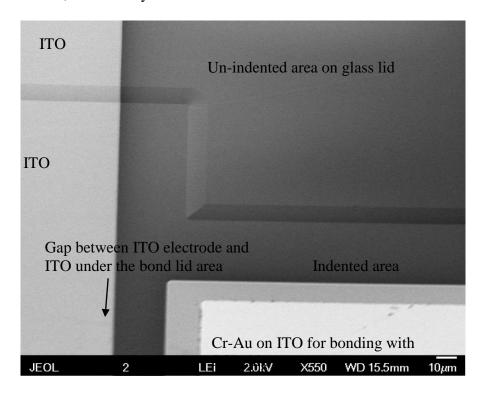

| Figure 3-18 | S: SEM image illustrating the indent area in the glass and the connection of the ITO electrode over the indent                                                   | 61 |

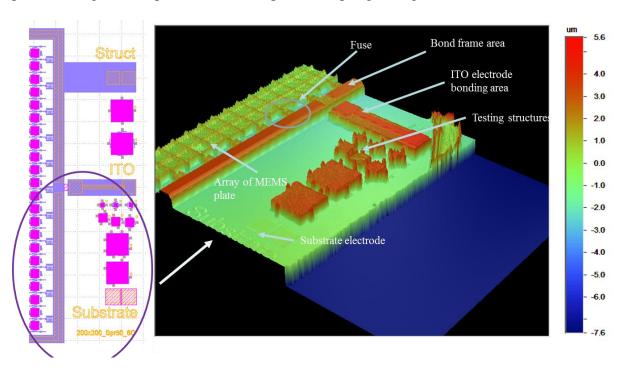

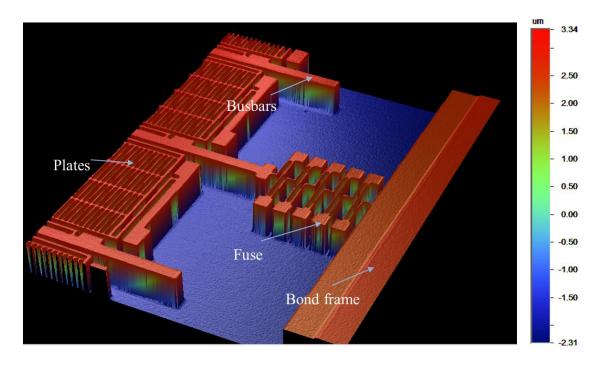

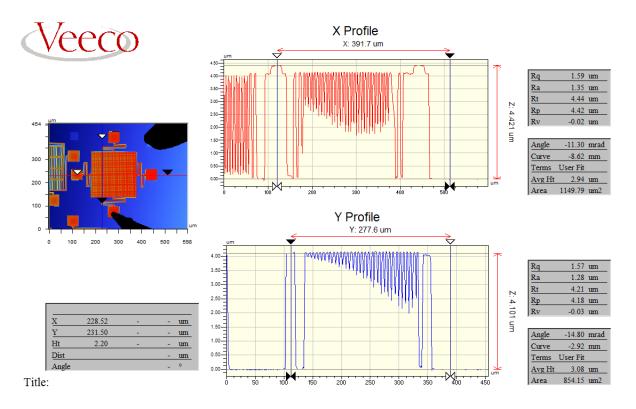

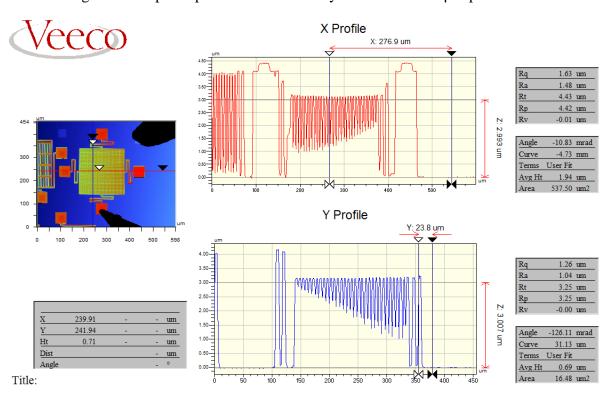

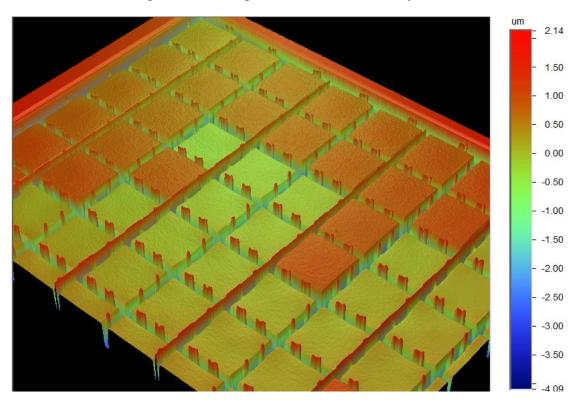

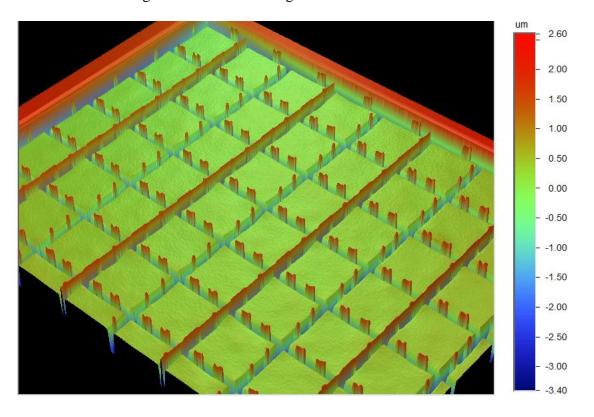

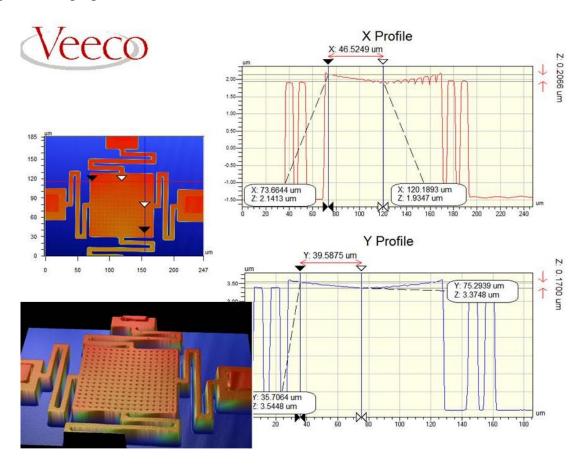

| Figure 4-1: | At left is the snapshot of the mask layout; at right is the optical profilometer image of the test area of a fabricated wafer.                                   | 65 |

| Figure 4-2: | 3D optical profilometer image of fuse element in the circuit                                                                                                     | 65 |

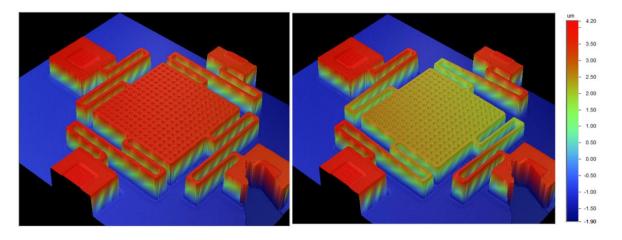

|                                                                  | 100 x 100 µm MEMS plate with four serpentine springs showing the optical profilometer image at 0 V (left) and at 9 V (pulled in) (right).                                                                                                                 | 66                                   |

|------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

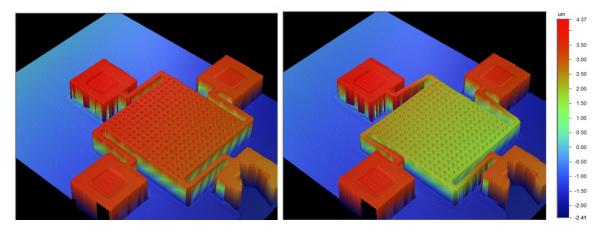

| _                                                                | 100 x100 μm plate with short spring showing the optical profilometer image at 0 V (left) and at 45 V (pulled in) (right)                                                                                                                                  | 67                                   |

| Figure 4-5:                                                      | Optical profilometer 2D analysis of 200 x 200 µm plates at 0V                                                                                                                                                                                             | 68                                   |

| Figure 4-6:                                                      | Optical profilometer 2D analysis of 200-µm plates at 4 V                                                                                                                                                                                                  | 68                                   |

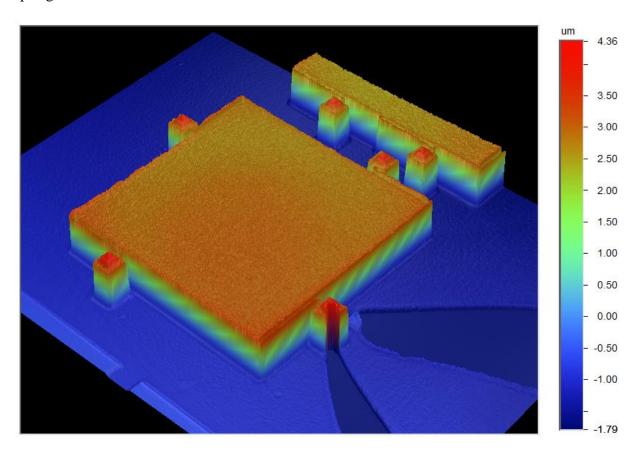

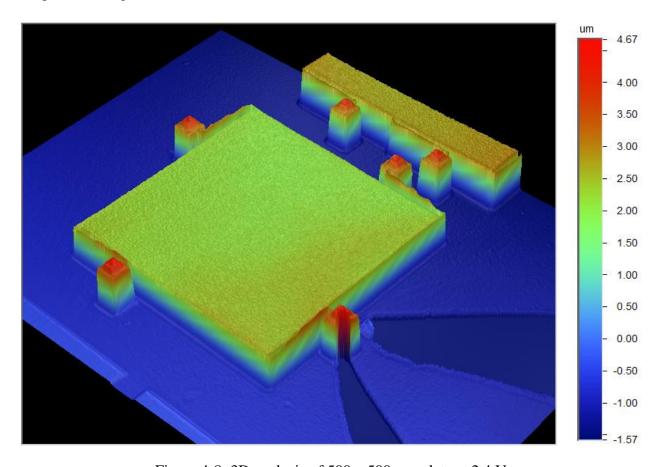

| Figure 4-7:                                                      | BD analysis of 500 x 500 μm plate at 0 V                                                                                                                                                                                                                  | 69                                   |

| Figure 4-8:                                                      | BD analysis of 500 x 500 μm plate at 2.4 V                                                                                                                                                                                                                | 70                                   |

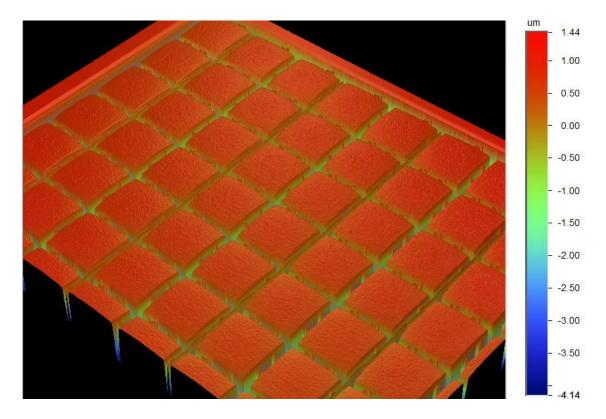

| Figure 4-9:                                                      | One-quarter of the MEMS array at 0 V                                                                                                                                                                                                                      | 72                                   |

| Figure 4-10:                                                     | One-quarter of the MEMS array at 4.2 V, where 500 x 500 µm MEMS plates with 8 springs were partially pulled in                                                                                                                                            | . 72                                 |

| Figure 4-11:                                                     | MEMS array at 9 V, where all the MEMS plate are pulled in                                                                                                                                                                                                 | 73                                   |

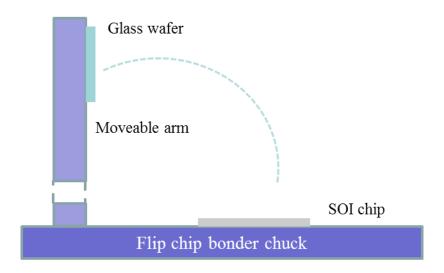

| Figure 4-12:                                                     | Setup for flip chip bonding of the SOI and the glass chip                                                                                                                                                                                                 | 75                                   |

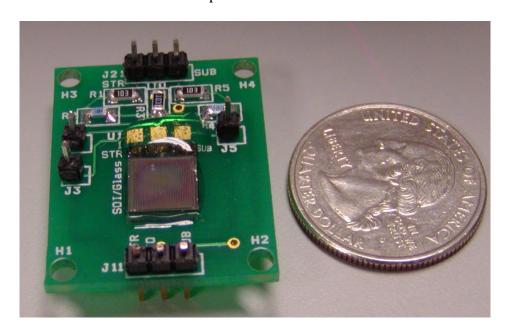

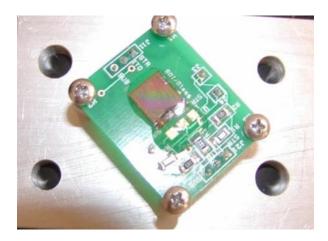

| Figure 4-13                                                      | Bonded MEMS chip on the PCB                                                                                                                                                                                                                               | 76                                   |

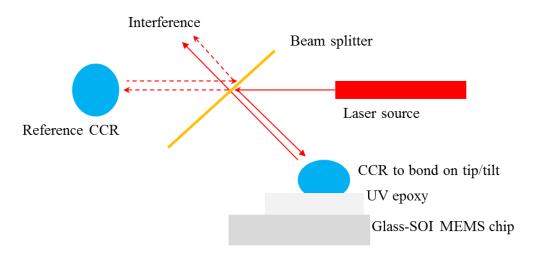

| Figure 1-14:                                                     |                                                                                                                                                                                                                                                           |                                      |

| riguic 4-14.                                                     | Block diagram of interferometric alignment setup for precise alignment of SOI/glass chip on PCB to CCR                                                                                                                                                    | . 77                                 |

|                                                                  |                                                                                                                                                                                                                                                           |                                      |

| Figure 4-15:                                                     | SOI/glass chip on PCB to CCR                                                                                                                                                                                                                              | . 78                                 |

| Figure 4-15:                                                     | SOI/glass chip on PCB to CCR                                                                                                                                                                                                                              | . 78<br>. 78                         |

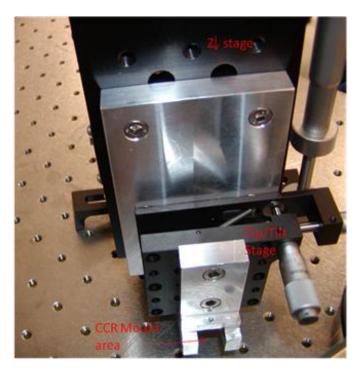

| Figure 4-15: Figure 4-16: Figure 4-17:                           | SOI/glass chip on PCB to CCR  Aluminum plate to hold the SOI/glass chip PCB  Mechanical fixture to mount the CCR and provide tip/tilt and translation using micrometers  Dispensing water to understand the amount of liquid needed to ensure             | . 78<br>. 78<br>. 80                 |

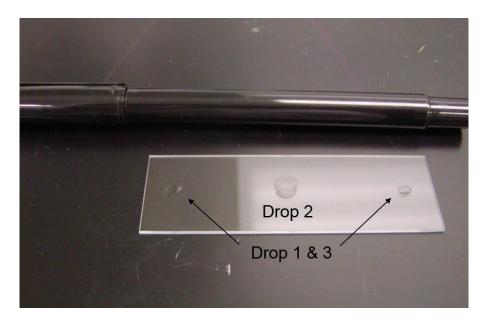

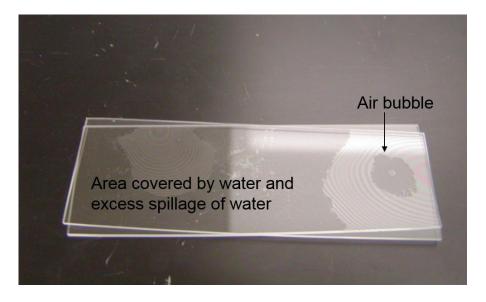

| Figure 4-15: Figure 4-16: Figure 4-17: Figure 4-18:              | SOI/glass chip on PCB to CCR  Aluminum plate to hold the SOI/glass chip PCB  Mechanical fixture to mount the CCR and provide tip/tilt and translation using micrometers  Dispensing water to understand the amount of liquid needed to ensure no spillage | . 78<br>. 78<br>. 80                 |

| Figure 4-15: Figure 4-16: Figure 4-17: Figure 4-18: Figure 4-19: | Aluminum plate to hold the SOI/glass chip PCB                                                                                                                                                                                                             | . 78<br>. 78<br>. 80<br>. 80<br>. 81 |

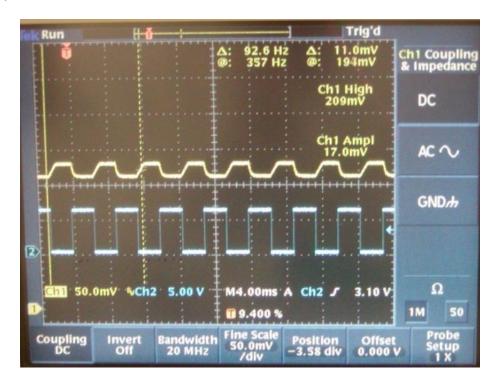

| Figure 4-22: Modulation signal to the CCR (bottom trace in blue) and the retroreflected signal from the CCR (top trace in yellow)                                                             | 85  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| signal from the Cert (top trace in Jenow)                                                                                                                                                     | 05  |

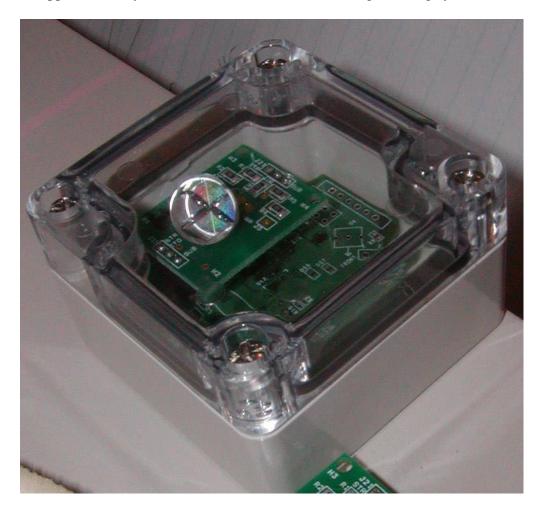

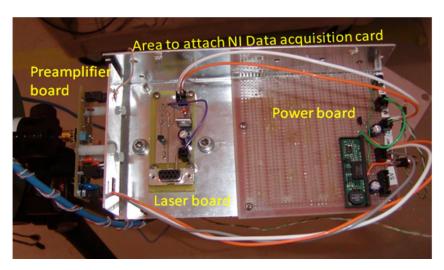

| Figure 5-1: Assembled, functional sensor board.                                                                                                                                               | 87  |

| Figure 5-2: Complete transmitter unit packaged with the CCR board and the sensor board.                                                                                                       | 88  |

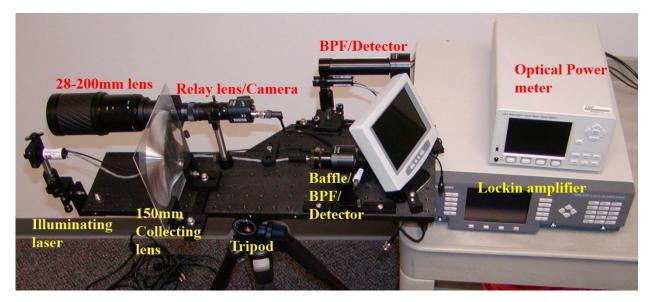

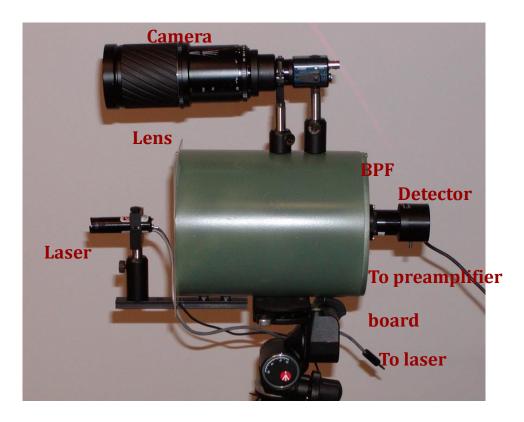

| Figure 5-3: Prototype receiver with baseband and high speed communication using COTS and test instrumentations                                                                                | 90  |

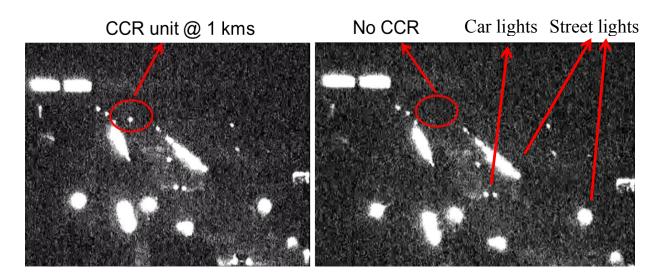

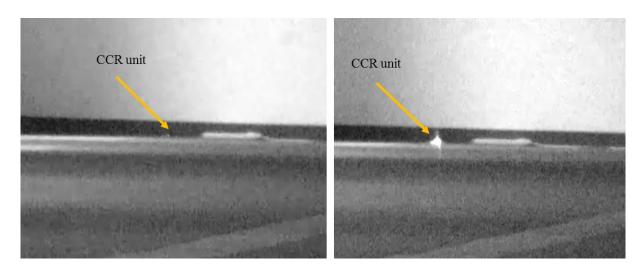

| Figure 5-4: CCR unit visible from a 1.0 km range.                                                                                                                                             | 91  |

| Figure 5-5: Testing at 56 m with the CCR on the ground and the view from the camera                                                                                                           | 93  |

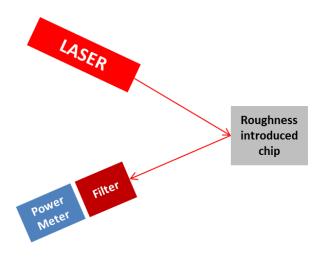

| Figure 5-6: Set up for reflectivity test of a roughness-introduced chip.                                                                                                                      | 95  |

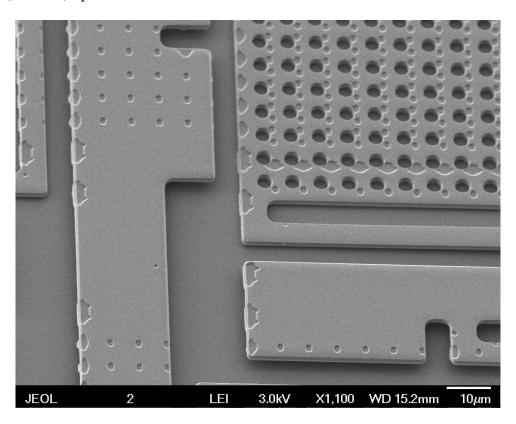

| Figure 5-7: SEM image of a triple exposed SOI chip to improve scattering efficiency                                                                                                           | 96  |

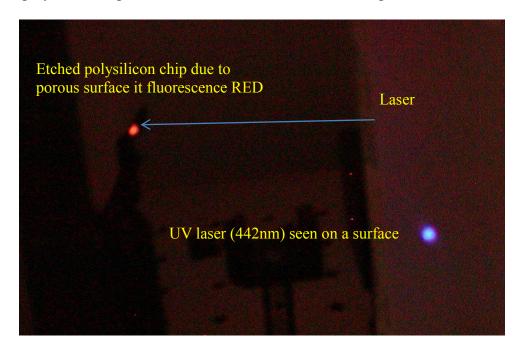

| Figure 5-8: Fluorescence by nanopores when illuminated with He-Cd laser                                                                                                                       | 100 |

| Figure 5-9: Optical image illustrating the difference between an HNA-treated chip to an untreated chip.                                                                                       | 102 |

| Figure 5-10: Optical profilometer data illustrating that the MEMS plate fabricated on polysilicon had significant bow after the release of mirrors due to intrinsic stress.                   | 103 |

| Figure 5-11: Front section of the receiver unit.                                                                                                                                              | 105 |

| Figure 5-12: Rear end of the receiver unit, illustrating the improvements made towards making the high speed receiver system compact and portable                                             | 105 |

| Figure 6-1: Assembled transmitter unit with temperature, humidity, and 2-axis magnetic sensors; microcontroller; infrared remote control receiver; field configuration jumpers; and a battery | 108 |

#### **ABSTRACT**

This dissertation presents a free-space, long-range, passive optical communication system that uses electrostatically modulated microelectromechanical systems (MEMS) structures coupled with a glass total internal reflection (TIR)-type corner cube retroreflector (CCR) as a non-emitting data transmitter. A CCR consists of three mirrors orthogonal to each other, so that the incident beam is reflected back to the incident beam, source. The operational concept is to have a MEMS modulator fusion with TIR CCR, such that the modulators are working periodically to disrupt the evanescent waves at the air interface of one of the three back glass faces of a TIR CCR. The MEMS chip has two primary components: (1) an array of movable light-scattering silicon structures with nano roughness and (2) a glass lid with a transparent conductive indium tin oxide (ITO) film. The MEMS structures are bonded to a glass lid using flip-chip bonding. Once bonded, the MEMS structures can be modulated either toward or away from the glass lid, thus disrupting evanescent energy delivered from a probing laser beam. The MEMS structure is precisely bonded to the TIR CCR with an accuracy of 10-30 arc-seconds using a Michelson interferometry feedback system. This is a novel step by which an existing passive commercial CCR can be converted into a modulating active CCR. This CCR-MEMS unit acts as the key element of the transmitter. To illustrate the concept of a low-power, unattended, sensor-monitoring system, we developed a sensor board containing temperature, humidity, and magnetic sensors along with a microprocessor and other electronics. The sensor board and CCR board are packed together and act as the transmitter unit. We developed a benchtop system and

an improved portable receiver system. The receiver system contains the laser (as source), a collimating lens (to collect retroreflected signal), an optical, narrow band pass filter, and a detector. The detector signal was amplified and filtered and sent either to the oscilloscope, a lock-in-amplifier, or a laptop to display the sensor data. Using the receiver system, a sensor-CCR-based transmitter unit, and receiver with 635 nm as source, we achieved retroreflective communication over a distance of 300 m.

#### CHAPTER 1

# INTRODUCTION

Optical communication has been a mode of communication since medieval times. In the past, people used fire beacons to indicate an event, with eyes acting as receiver, and the beacon as transmitter [1]. Today, light sources such as light-emitting diodes (LED) or light amplification by simulated emission of radiation (laser) now have become the interrogating source and precise detector acts as receiver. If we need to convey only a trigger point or one specific event, optical devices like mirrors or reflectors can be used. For instance, the conveyer belt in a grocery store has a source/detector on one end and a reflector on the other, and the belt continues to run until an item interrupts the reflected signal. This system indicates an event (the item is there or not there), and the movement of the conveyer belt is based on the event. An automatic garage door uses a similar mechanism, with a reflector on one end and a source/detector on the other. If there is any obstruction between the source and reflector, the garage door does not close. Retro-reflectors are also used on streets so that drivers can clearly see the road.

# 1.1 Objective and Background

In the above examples, a reflector is used as a passive device to indicate a specific event. If we wish to perform optical communication using a reflector, we can design a mechanical shutter that blocks the light to indicate a binary position (say "0") and pass the light to indicate the other position ("1"). Mechanical shutters controlled by digital electrical signals are easily available in the market and would be a one of the ways to perform optical communication. If the mirror has the right material, reflectivity, and performance, optical communication can be

performed over a long range for various wavelengths of interrogating sources. We can increase shutter speed to perform at high data rate communication. This system and setup are potentially useful at a macroscopic level, where the transmitter is larger than 3 cm<sup>3</sup>, weighs more than 300 grams, consumes power in the mW-W region, and communicates in the 10- 100 msec range.

This macroscopic level setup may be good for some applications; however, applications such as inter-satellite communications, tags for inventory tracking, military applications, environmental monitoring, clandestine communication, and several others currently use active RF link communication. Using RF communication has drawbacks such as the possibility of jamming, bandwidth limitation, large antenna size, and high power consumption [2]. To overcome these drawbacks and have an alternative communication system, there presents a need for a compact (<1 cm<sup>3</sup>), light (< 50 grams), low-power ( $\mu$ W –  $\mu$ W), high-speed ( $\mu$ Sec –  $\mu$ Sec), cost-effective optical transmitter for long-range optical communication. This dissertation aims to provide insight in to one such compact, light, low power, high speed, cost effective optical communication method.

Micro electro mechanical systems (MEMS) is a renowned field in which mechanical or electrical actions are performed by providing actuation at the micron scale. Small devices in the range of 1 to 1000 µm are fabricated using the principles of semiconductor fabrication. The two major techniques used in MEMS fabrication are surface micromachining and bulk micromachining. In the former technique, layers of materials are deposited on a silicon wafer and etched to form MEMS devices. In the latter technique, the silicon wafer is etched and devices are formed. The field in which MEMS components are used for optical systems (MOEM) is an upcoming field, and several MOEM sensors are currently available in the commercial market. Texas Instruments' DLP mirror [3] and the deformable grating modulator developed at Silicon

Light Machines [4] are a few examples of optical MEMS systems. This dissertation describes the design of a MEMS chip that is precisely aligned to a commercial high-precision optical retroreflector, resulting in a transmitter that is used for optical communication.

# **1.1.1** Corner Cube Retroreflectors (CCR)

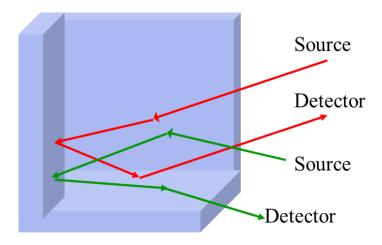

In the above examples the source and detector are on different sides. If we use one or two mirrors as the reflectors, then the positions of the source and detector are fixed, as for every incident angle there is a different reflected angle. This makes the sensor incident-specific, and the position of the detector becomes extremely crucial. In a CCR we use three mirrors that are orthogonal to each other and when the incident beam reflects off all three mirrors, then the retroreflected beam will be parallel to the incident beam, as shown in the optical ray from source to detector in Figure 1-1.

Figure 1-1: Hollow CCR

CCRs have found applications in numerous areas [2, 5-10]. For instance, an array of CCRs placed on the moon by Apollo astronauts [11] helps us determine the distance between the earth and moon at all times with great accuracy. One can measure the time it takes for the retroreflected beam to travel back from the base station at earth and depending on the light transmit time, one can estimate the distance between the base and the retroreflector on moon.

[11]. CCRs are readily available through commercial vendors like Thor Labs, 1 Edmund Optics, 2 and other optical vendors. CCRs are available in two major formats: hollow CCRs and total internal reflection (TIR) CCRs.

#### 1.1.2 Hollow CCR

In hollow CCRs, three flat mirrors are precisely aligned and bonded perpendicular to one another as shown in Figure 1-1. Hollow CCRs with Au and Al coating are available for enhancement in specific wavelength ranges and come in various sizes. There is no bulk material absorption or chromatic aberration, as the optical path between the mirrors is in air [12, 13]. A hollow CCR has a wide range of acceptance angles, restricted only by the geometry of the entrance aperture, making it less affected to the angular position of the incident beam. Broadband hollow reflectors from Newport<sup>3</sup> have an acceptable incident beam range of 180° [12, 13]. Depending on the placement of the CCR, there is a chance it will be covered with dust and moisture if left outside, which may affect the intensity of the retroreflected beam.

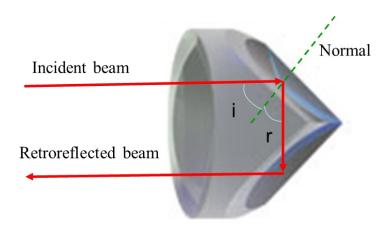

# 1.1.3 Total Internal Reflection (TIR) CCR

In a TIR CCR, a solid piece of optical material (such as BK7) is polished, leaving a highquality optical aperture and three orthogonal reflective faces (often these faces are coated with a metal to provide high reflectivity and acceptance angles similar to hollow CCRs) [12, 13] When uncoated, a CCR relies on the TIR effect to produce the three orthogonal reflectors. When the incident light angle exceeds the glass-air critical angle, then the incident beam is reflected within the CCR's glass, as shown in Figure 1-2. The limitation of the TIR CCR is that the range of acceptance angle is limited and dependent upon the refractive index of the glass.

<sup>&</sup>lt;sup>2</sup> Edmund Optics, Barrington, NJ

<sup>&</sup>lt;sup>1</sup> Thorlabs Inc, Newton, NJ

Figure 1-2: Total internal reflection CCR

# 1.2 Literature Review

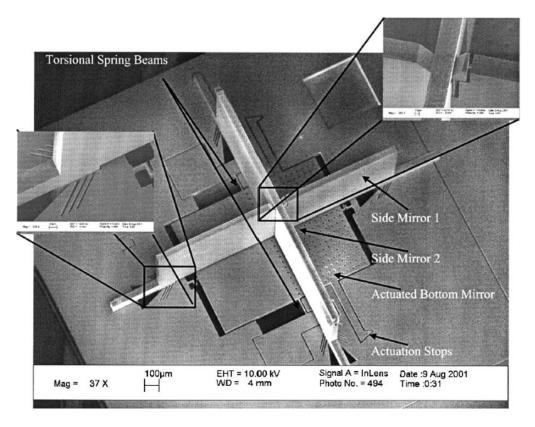

The ability to retro reflect light back to the source makes CCR a lucrative optical device, one possibility is miniaturizing and bonding the mirror and having the ability to slightly misalign one of the mirror makes it a feasible research interest. Several research groups are looking to develop MEMS CCR for long range low power communication. One of the earliest research work to develop MEMS CCR used MEMS mirrors fabricated using a surface micromachined polysilicon MEMS process. Pister and his group designed hollow CCR in MEMS scale where two 250 µm square mirrors were designed and were vertically aligned using his special hinge technique [14], the third mirror had the ability to actuate using electrostatic actuation [6, 15]. The work demonstrated a communication range of 2 m using a 4.7 mW 670 nm laser at 500 Hz or 1k bps data rate and electrostatic voltage of 10-15 V to modulate the electrostatic mirror. Analysis was done to understand the key parameters required for long-range communication, non-flatness and misalignment of the mirrors seemed to be two major causes for low range of communication. The radius of curvature of the mirrors should ideally be  $\infty$ . For optical communication range of 1 km, it is required a radius of curvature of 50 cm or higher [6, 16, 17]. Misalignment of the mirrors seems to be their major limiting factor for long-range communication over1 km, the

mirrors need to be aligned by 0.5 mrad (103 arc-second) or better, and a receiver of 500 mm is required to collect the retroreflected signal.

Figure 1-3<sup>4</sup>: Automated assembled MEMS CCR [17]

To improve mirror flatness, mirrors were later fabricated on single crystal silicon or structure layer of silicon on insulator (SOI) wafers. A thin layer of (50 nm) gold was deposited to improve the reflectivity of mirrors in some of the visible band. Initially the mirrors were aligned manually; later an automated alignment method was used. An alignment accuracy of less than 1 mrad (200 arc second) [6, 17, 18] was achieved on a 250-µm-square mirror. The electrostatic drive voltage was cut down from 10 V to 5 V and, using a 0.8 mW, 0.1 mrad (20 arc second) divergence, 632.8 nm laser, communication of 180 m was achieved at 200 Hz or 400 bps [17,

المنارة للاستشارات

<sup>&</sup>lt;sup>4</sup> Image was published in IEEE Micro Electro Mechanical System 2002, DOI: (10.1109/MEMSYS.2002.984332) and permission to use is included in Appendix A

18]. An order of magnitude improvement in communication range was made from the previous version to the current version. Energy consumption of 19-40 pJ per bit was reported, and total power consumption of the system was 1.7 mW [17]. This concept of developing a MEMS based CCR on electrostatic actuation method for unattended sensor monitoring concept from the above group was bought by a commercial company that intended to do low-power node-to-node communication using the MEMS CCR, to provide power to the CCR chip along with sensors it was bonded to a CMOS IC and solar cell array in a 16 mm<sup>3</sup> form factor [18].

In another publication, a self-assembled method using melting of resist was used to assemble the mirrors of the CCR. The CCR mirrors were aligned with an accuracy of 0.18° (~650 arc second) [19]. The drive voltage for these self-assembled mirrors fabricated using bonded silicon on insulator (BSOI) wafers had an actuation voltage of 30V and signal to noise ratio of 30 dB [19]. The communication range performance of the fabricated CCR was similar to that of the previously mentioned CCRs.

Similar to the above style of CCR, one of the groups fabricated piezoelectric actuators as the horizontal mirrors. They fabricated 300-µm vertical mirrors by etching doubly bonded SOI wafers using KOH. These vertical mirrors were then diced and manually bonded to horizontal mirrors. A novel design minimized the effect of residual stress from the PZT film on the horizontal mirrors, and a 5 V signal on the horizontal mirror was sufficient to displace the mirror by 1.37°. Alignment accuracy of 0.13° (~450 arc second) between the mirrors was reported, and an optical communication of 5 m at 2.5 kHz was achieved [20].

One of the groups working on long-range communication used a TIR CCR and developed a technique using multiple quantum well modulators (MQWM). Modulators were fabricated using layers of InGaAs/InAlAs quantum well on InP. The transparency or color of the

film (well) changed when voltage (15 V) was applied. This MQWM was attached to a 0.63-cm-diameter commercial TIR CCR with 10 arc second (0.048 mrad) alignment accuracy. A communication range of 2 km at 5 Mbits/s (~ 2.5 MHz) was achieved using a 1550 nm laser operating at 4.2 W. A set of five modulators was arranged in a mechanical fixture, and 2 km communication was demonstrated across Chesapeake Bay, with each modulator consuming 200 mW [7, 21, 22]. Although this method has a long range of communication, using an electro-optic modulator consumes a lot of power (0.2 W per modulator compared to 1.7 mW electrostatic actuation of a MEMS mirror).

One of the other groups used an array of TIR-based CCRs and applied pressure on an elastomeric material, such that the elastomeric material is close to one of the reflecting mirrors of the TIR CCR. A thin film close to the mirror causes frustration of the total internal reflection, which reduces the intensity of the retroreflected signal. A 0.9 m CCR array was selected and 2% carbon loaded PDMS gel was used as the elastomeric material. Pressure of 100 kPa was applied to the film, and a 1% change in retroreflectance was observed [23, 24]. This process was slow and inconsistent because the gel took time to bond and debond to the CCR when pressure was applied.

One of the research groups demonstrated the use of CCR in a magnetometer application, where a change in magnetic field between 820 A/m and 6 kA/m was detectable. A hollow MEMS CCR was fabricated with one of the mirrors on a movable torsion arm connected to a magnet. As the magnetic field changed the torsion arm would move, causing the movable CCR mirror to deflect from its original position. This application is suitable for detecting large amounts of ferrous material (e.g., jeeps, tanks, weapons) [8].

Several research groups have been working on understanding the challenges in long-range optical communications, such as atmospheric turbulence and incident beam divergence.

One researcher illustrated that in a retroreflected beam based communication system the retroreflected beam spot has a standard deviation of about 1 cm for a communication of 300 m and about 10 cm for a communication up to 500 m in turbulent measurement conditions [25-27] and suggested that the effect of turbulence on the beam spot becomes significant as the range exceeds 1 km. Other groups have focused on different communication schemes, and one researcher suggested that using an on-off keying method and array of reflectors with one photodiode to receive all the retroreflected signal would yield better signal-to-noise ratio (S/N) than multiple detectors[28-31]. One of earliest papers describing communication through retroreflected power concluded that the S/N of optical communication would be better than that of radar communication [2, 29, 30].

# 1.3 Previous Work at USF

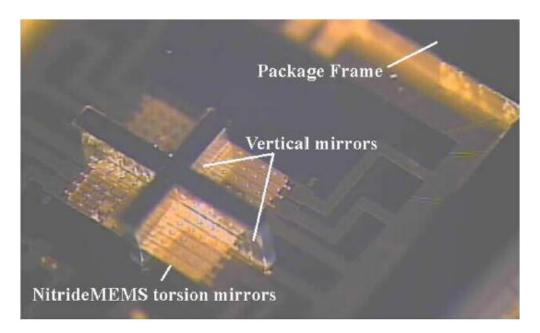

In our earlier work at the University of South Florida, we started with a hollow MEMS CCR, where the vertical mirrors were fabricated using deep reactive ion etching (DRIE) etching of a double side polished silicon substrate. To improve the flatness and roughness of the DRIE surface, they were treated with KOH+IPA etching. Finally they were metallized and bonded to a single side polished silicon wafer with horizontal mirror. Using bulk micromachining we fabricated electrostatically actuated mirrors using a custom developed process called NitrideMEMS. In this process, 2-µm silicon nitride was the structural material with a sacrificial gap of 3 µm. Top and bottom electrodes were deposited using Cr/Au or Ti/Au layers. A completely fabricated MEMS CCR is shown in Figure 1-4. Using this process, we fabricated the CCRs with alignment accuracy of 0.1° and surface roughness of 10 nm [32]. We achieved a

communication range of 10-30 m at 1 kHz data rate and applied actuation voltage of 6 V on the mirrors to move the mirrors from on to off position [5, 32-35].

Figure 1-4<sup>5</sup>: Hollow CCR fabricated with 250-μm-long vertical mirror and movable horizontal mirror [32, 33]

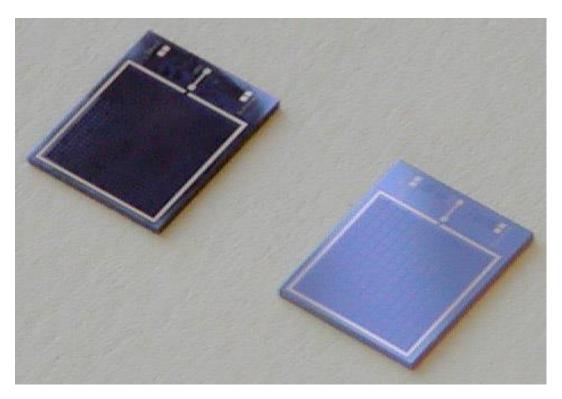

A transmitter unit 30 x 30 x 6 mm was designed to incorporate the CCR, mechanical switch, microprocessor, temperature/humidity sensor, indicator LEDs, and thin batteries as shown in Figure 1-5. The unit met all the above-mentioned criteria except the communication range; this was because the misalignment of mirrors in this system was  $\sim 0.5^{\circ}$ , which was sufficient to cause the retroreflected signal to be undetected after 30 m [5, 32, 36].

From the research mentioned above and the literature review, we realize that miniaturizing traditional hollow CCRs using MEMS concept was difficult. As aligning the MEMS mirrors to precise orthogonality was a major issue, causing low communication range. When TIR CCRs were used with a MQWM modulator, they were able to communicate over long

<sup>&</sup>lt;sup>5</sup> This image was published in IEEE MEMS, NANO and Smart Sensors 2005, DOI: (10.1109/ICMENS.2005.50) and permission to use is included in Appendix A

ranges but consume many watts of power. The work presented in this dissertation illustrates a different approach taken to improve the communication range and develop a compact (1 cm<sup>3</sup>), low-power (10 mW), moderate data rate (5 kHz) optical communication system.

Figure 1-5<sup>6</sup>: Front and back side of a packaged MEMS CCR with temperature sensor [36]

# 1.4 Organization of the Dissertation

This dissertation is divided into four major parts: transmitter and receiver design calculations, design and fabrication of MEMS chip for transmitter; bonding and testing and development of hybrid MEMS-CCR transmitter; and development of the receiver unit and improvements. In the second chapter we discuss the CCR selected and the concept of evanescent wave coupling, empirical calculations for design of transmitter and receiver system. Chapter 3 details the process development, followed by design and fabrication of the MEMS chip. Chapter 4 discusses in detail testing of the fabricated MEMS structure and then the precise bonding of the MEMS and CCR and benchtop optical testing results. Chapter 5 discusses the development of transmitter/receiver unit and improvement made in the MEMS chip and optical communication results. Finally, chapter 6 concludes the discussion and provides future recommendations.

<sup>&</sup>lt;sup>6</sup> This image was published in SPIE Defense and Security, 2007. DOI: (10.1117/12.721203) and permission to use is included in Appendix A

#### **CHAPTER 2**

# DESIGN AND CALCULATIONS OF OPTICAL, MEMS CHIP AND SYSTEM PARAMETERS

In the previous chapter, we learned that several researchers are looking to develop a compact, low-power, high-speed, lightweight transmitter for optical communication. The CCR has been identified as one of the key transmitter components, and most research uses a traditional MEMS method to fabricate and assemble the reflectors. We also plan to use MEMS technology to assist us in creating a transmitter with those important qualities to perform long-range optical communication. However, our approach uses a MEMS chip hybridized with a commercial CCR. In this chapter we first lay out the key CCR parameters for long-range communication and then explain our MEMS technology and commercial CCR hybrid concept for the transmitter. Next, we discuss the CCR selection. Finally, we perform optical and electrical calculations to design the optical system and the MEMS chip.

# 2.1 Factors Impacting Range in a CCR-Based Communication System

Numerous factors play an important role in determining the range of an optical communication system based on CCR. Source wavelength, acceptance angle, mirror roughness, mirror coating, and atmospheric turbulence all affect communication range, but the two most important factors that dictate the range of optical communication are orthogonality and flatness of the mirrors, as discussed below.

# 2.1.1 Orthogonality of the Mirrors

A CCR has three mirrors, and the relative orthogonality of these mirrors is extremely critical for long-range optical communication. Commercially available CCRs have orthogonality (or misalignment) accuracy between the three mirrors of 1-10 arc-seconds (0.00277°), almost 20 times better than any reported MEMS CCR device. It is extremely challenging to fabricate a miniature MEMS-based CCR with one active (movable) mirror and align them to an accuracy of 1-10 arc second (0.00277°). This level of alignment accuracy is important because it enables capture of the retroreflected signal with a reasonable size detector [16, 37]. As illustrated in Figure 2-1, if the CCR has a misalignment ( $\delta$ ), then for an optical communication range of L, the offset (x) of the CCR's retroreflected signal due to misalignment is represented as

$$x = L \tan \delta. \tag{2.1}$$

If we are able to bond the CCR mirrors with an accuracy of 30 arc-seconds, then for an optical communication distance of 1 km, the offset in the retroreflected signal would be 145 mm, which means that at least a 145 mm wider detector is required to capture the retroreflected signal (this is without considering beam divergence). As seen in Equation 2.1, the misalignment in the mirrors directs the detector size. A 10-30 arc-second misalignment enables a reasonably sized (145 mm) receiver optics that can capture most of the retroreflected signal.

Figure 2-1: CCR mirror misalignment causing the retroreflected signal to disperse at long ranges

#### 2.1.2 Flatness of the Mirrors

The second most important factor in determining optical communication range is the flatness of the mirrors. The researchers at UC Berkley [6, 16, 17] performed optical modeling and determined that CCR mirrors need to have a 100-cm radius of curvature for optical communication over 1 km. Their paper explains that if the radius of curvature of the mirror is below 50 cm, then the quality of the retroreflected signal diminishes significantly, and that below 20 cm, the mirror is not suitable for long range optical communication. The paper compares retroreflected signals from four different radii of curvature: 20 cm, 50 cm, 100 cm, and  $\infty$  and concludes that a 50-cm curvature gives a 1.5x improvement in the amplitude of the retroreflected signal, and that using a mirror with a 100-cm curvature creates a 2x improvement as compared to a mirror with a 20-cm radius curvature. A mirror with infinite curvature is an ideal mirror, and it retroreflects the beam entirely. Commercial CCRs are available with curvatures from 100 cm to  $\infty$ ; in our design we plan to use mirrors with a radius of curvature better than 100 cm.

#### 2.1.3 Other Factors

Source wavelength, CCR material, incident angle, size of CCR, incident laser power play an important role in determining the system parameters. However, these are external factors and can be altered to make the overall communication system effective. We will discuss more about these factors and their impact in later sections. Weather conditions and suspended air particles in the atmosphere causes attenuation and scattering of the retroreflected signals. The Mie scattering model [7, 25, 26, 38], examines how environmental conditions affect line-of-sight optical communication, at different ranges. One of the researchers developed a model to illustrate how turbulence affected the retroreflected signal, and concluded that there is deviation of beam by 1 cm at 300 m and 10 cm at 500 m [25, 38].

# 2.2 CCR MEMS Hybrid Concept

From factors discussed above, we have concluded that there is a tight tolerance on the misalignment of the mirror and that the idea of making a completely MEMS-based CCR system with one movable mirror while maintaining precise orthogonality during the off state would be extremely challenging. Micromachining techniques provide an advantage by allowing the fabrication of miniature electro-mechanical structures. Commercial CCRs offer the precise alignment essential for long-range communication. By combining these two advantages, we can develop a hybrid commercial CCR-MEMS unit that will decrease the retroreflected signal in one state and allow it in another. Figure 2-2 illustrates such a unit.

Figure 2-2: Commercial CCR and MEMS chip concept

The idea is to develop a MEMS chip that can precisely bond to the TIR-based CCR and shift (or extend) the retroreflecting plane of the TIR so that a MEMS structure can, upon actuation, be brought close enough to attenuate the retroreflected signal by scattering the light at the extended surface. Electrostatic actuation is one of the methods we can use to position the MEMS structures close to the new TIR plane; we can also devise MEMS structures that will interact with the surface waves. We plan to pursue this concept by increasing our understanding

of the optical requirements for the communication system and then determining the requirements to develop the MEMS actuator.

# 2.2.1 Principle of TIR and Evanescent Wave Coupling

Total internal reflection (TIR) occurs when an incident light from above the critical angle passes through a medium of higher refractive index into a medium of lower refractive index, causing all the light to be reflected at the boundary of indices. During reflection at the glass-air interface, evanescent waves are formed in the air near the surface of the glass (Figure 2-3). These evanescent waves decay exponentially perpendicular to the reflection plane, as represented in Equation 2.1 [39-41]. If not disturbed, the evanescent waves then reflect back along with the internal reflected beam. If we disrupt these evanescent waves, then the intensity of the retroreflected beam diminishes. This attenuation in the reflected signal illustrates the difference between the un-scattered and scattered mode. Since bonding the MEMS structure close to the TIR plane is not possible, a glass lid with MEMS structures capable of moving in-and-out of plane was bonded to one of the sides of TIR CCR. The glass lid can also provide inherent environmental protection to the modulating MEMS structures.

Figure 2-3: Total internal reflection occurs when the incident angle is greater than the critical angle.

$$I(z) = I_0 e^{-z/d} (2.2)$$

$$d = \frac{\lambda_i}{4\pi n_1 \sqrt{\sin^2 \Theta_i - \sin^2 \Theta_c}} \tag{2.3}$$

$$\Theta_c = \sin^{-1} \left( \frac{n2}{n1} \right) \tag{2.4}$$

We understand that the evanescent waves occur close to the surface and decay exponentially as from Equation 2.2 [37, 39, 40, 42]. To calculate the depth of penetration for waves in perpendicular distance z from the interface, let us consider Equation 2.3 [37, 39, 40], where d is the penetration depth of the waves,  $\lambda_i$  is the wavelength of the incident beam,  $\Theta_i$  is the incident angle,  $\Theta_c$  is the critical angle, nI is the refractive index of BK7 is 1.515 for 635 nm light, and n2 is the refractive index of air (1 for all wavelengths). The critical angle can be calculated from Snell's law using Equation 2.4 [40]. Using the data mentioned above calculations show a critical angle of 41.3° for a wavelength of 635 nm. Penetration depth of the evanescent waves for a 635 nm source, for instance with an incident angle of 43° is 195 nm, and this evanescent wave decay increases as the incident angle becomes closer to the critical angle. By bringing the MEMS scattering structures within the penetration depth, we can disrupt the evanescent beam and reduce the intensity of the retroreflected beam. This scattering of evanescent waves forms the basis of our modulator's operation.

# **2.2.2** Determination of Penetration Depth for Different Wavelengths

To understand how fast the evanescent beam decays and what effect it has on the retroreflected signal we can compute that from Equations 2.2 and 2.3, one of our colleagues developed a MATLAB program using a more detailed analysis mentioned in Book: *Principle of Optics* [40]. This program is to compute reflection of an incident beam (at 45°) on a mirror when a scattering object is bough in the close vicinity (defined as gap) to the reflection plane.

Figure 2-4: Reflectivity at different wavelengths illustrating how reflected beam penetration depth changes with gap. Top shows 0 to 1.5  $\mu$ m, middle zooms in to show 0 to 0.5  $\mu$ m, and the bottom further zooms in to 0 to 0.2  $\mu$ m for a 45° incident beam

Using this code, the reflection versus gap for three different wavelengths were plotted (Figure 2-4). The top plot in the figure is a zoomed out view showing a gap from 0 (touching) to a 1.5  $\mu$ m gap, and as we see from the plot, if the MEMS interacting structure is more than 1  $\mu$ m away, then almost 100% of the light is reflected back. The middle plot is zoomed into the 0 to 0.5  $\mu$ m range and shows that the reflected energy of the 635 nm wavelength is almost 95% at 0.5  $\mu$ m, but it drops almost to 60% by 1550 nm, which indicates that the chances of detecting a change in reflectivity is much higher at 1550 nm than 635 nm for the same MEMS movement. The final plot is zoomed in from 0 to 0.2  $\mu$ m to illustrate how the reflectance changes in that nanometer range. So, if we can get scattering structures to 200 nm or closer we should detect change in reflectivity for 635 nm, however there is benefits for using higher wavelengths to produce deeper modulation contrast.

# 2.2.3 Incidence Angle

As seen from Equation 2.3, the penetration depth of evanescent wave is indirectly proportional to the incidence angle. To understand the effect of incident angle, we plotted the penetration depth (or evanescent wave decay) versus incident angle for three different common semiconductor laser wavelengths (635, 980, and 1550 nm) in Figure 2-5. The critical angle was determined from the refractive index of our working CCR material, BK7 (n = 1.515). From Figure 2-5, we inferred that the penetration depth decreases if the incident angle is not close to the critical angle. If we have MEMS structures at 200 nm from the reflective plane, then for 635 nm wavelength, the incident angle is limited from 41.35° to 44°, which is a short band to target. For 1550 nm wavelengths, the acceptable incident angle range increases to 50° for the same gap. For the purposes of our experiment, we feel we can have incidence beam closer to 43°, after spotting the CCR from camera. However, it will be difficult to target this narrow incident range for other practical applications.

As we learned in Chapter 1, hollow CCRs have high incident (acceptance) angle close to 180°. For TIR-based CCR, the acceptance angle is limited and based on material type, we can either have a CCR made of material with high refractive index (2.1-2.4) to accept broader incident signal. As seen from Figure 2-5 that higher wavelength beams will require fewer CCRs compared to lower wavelength beams, as higher wavelength have higher acceptance angle. Figure 2-6 charts the acceptance angle of the TIR limited CCR device for different CCR glass refractive index values. It illustrates that we will need CCRs made of material with a refractive index in the range of 1.515-2.175 in order to cover incident angles from 40-90°. The number of CCRs required to cover this incident angle range may differ based on the wavelength of the incident beam.

# Evanascent wave decay vs incidence angle for different wavelengths with 41.35° as critical angle

Figure 2-5: Evanescent wave decay vs incidence angle of different wavelengths with 41.35° as critical angle

Until now, we have been discussing incident and acceptance angles as if they were the same. However, TIR-based CCRs have a front face, and the reflecting TIR planes are at an angle, so calculations should compensate for the angle between the TIR plane and the front face. In the commercial CCR if the incident beam is normal to the front face, then it creates an incidence angle of 54.7° at the TIR plane. This incidence angle is higher than critical angle causing the beam to have TIR effect. We also performed calculations using optical coatings consisting of materials with higher refractive indices, either on the front face or mirror face of the CCR and that did not improve the acceptance angle.

#

Figure 2-6: Acceptance angle of TIR-based CCR vs. its refractive index

1.7

CCR Refractive Index

1.8

1.9

2.1

2.2

1.6

# 2.2.4 Selection of Commercial CCR

1.3

1.4

1.5

20 | 1.2

To make the final selection of the TIR CCRs, we looked at various vendor catalogs and discovered that TIR CCRs come in different sizes, angle tolerances, surface flatness, coatings, and other variations. To enable us to make a reasonably-sized MEMS chip that can be attached to the CCR, we chose a 12.7 mm diameter CCR. Several vendors sell similar TIR CCRs with diameter of 7.16 mm, so if we wanted to make our CCR unit smaller, we could. Our selection is made of an uncoated, BK7 material with a  $\lambda$ /8 flatness [12, 13]. Three different variations of angle tolerance were available, 1, 5, and 10 arc-second. We selected the 10 arc-second CCR, as they were inexpensive (less than \$20), reasonable for experimental purposes and should allow long range communication. As our process solidified, we considered going to a more accurate 1-arc-second angle tolerance mirror, however they are expensive (~\$300/each) and would increase the cost of the transmitter[12, 13]. Our final decision was to order an uncoated, 12.7 mm

diameter, BK7 material,  $\lambda$ /8 flatness, 10 arc-second angle tolerance CCR, and this is what we used for the experiments.

# 2.3 Requirements for the Receiver Unit

One of the most difficult tasks on the receiver end is to collect enough of the retroreflected signal since at long ranges even a slight misalignment of the CCR mirrors means that we need a large lens to collect all the signal. Even though we collimate the laser beam, there is still some beam divergence (0.5 mrad), which means that the beam at the CCR instead of a dot is like a spot. The spot size of the beam at the CCR can be calculated, and, depending on the misalignment in the CCR mirrors, the retroreflected beam size at different ranges can also be calculated. Using a laser source ( $\lambda$ ) of 635 nm and a CCR diameter (d) of 12. 7 mm, beam divergence ( $\Theta$ ) was calculated by Equation 2.5, where w is the radius of the beam at its narrowest point (also called the beam waist) and given by Equation 2.6 [40].

$$\Theta = \lambda/\pi w \tag{2.5}$$

$$w = d/2 \tag{2.6}$$

Since the beam divergence is the half angle representation, the total beam spread will be twice that angle. So, for the given CCR dimensions and communication range, the beam spread at the CCR is 6.37e-5 radians (13.13 arc-seconds). This means that if we want to see the spot at the receiver due to just the beam spread at the CCR for a given distance (d), then the spot size at the receiver due to CCR beam spread is given by s

$$s = \sqrt{w^2 + (\Theta d)^2} \tag{2.7}$$

Also, since there is an offset on the spot size due to misalignment in the CCR during bonding (presently around 30 arc-seconds in our final system and denoted by  $\delta$ ), the offset of the spot size at the receiver due to this misalignment is given by m

$$m = \sqrt{w^2 + (\delta d)^2} \tag{2.8}$$

This means we need a lens at the receiver that is large enough to collect all the optical light from the spot size and the offset, a diameter given by a

$$a = s + m \tag{2.9}$$

To enable the receiver system to be portable, we need to ensure that the collecting lens is of manageable size. From above, we understand that the misalignment of mirror plays an important role deciding the size of the collimating lens on the reflector, which would decide if the receiver is portable or not.

Table 2-1: Beam spot at the receiver after beam divergence 0.5mrad (100 arc second) and misalignment 30 arc second (0.15 mrad) due to CCR at different ranges

| CCR range (km) | Spot size @ receiver (mm) | Offset due to CCR misalignment (mm) | Spot size + offset (mm) |

|----------------|---------------------------|-------------------------------------|-------------------------|

| 0              | 12.7                      | 0.0                                 | 12.7                    |

| 0.1            | 14.2                      | 14.5                                | 28.8                    |

| 0.2            | 18.0                      | 29.1                                | 47.1                    |

| 0.4            | 28.5                      | 58.2                                | 86.6                    |

| 0.5            | 34.3                      | 72.7                                | 107.0                   |

| 0.6            | 40.3                      | 87.3                                | 127.5                   |

| 0.7            | 46.3                      | 101.8                               | 148.1                   |

| 0.8            | 52.5                      | 116.4                               | 168.8                   |

| 0.9            | 58.7                      | 130.9                               | 189.6                   |

| 1              | 64.9                      | 145.4                               | 210.4                   |

| 1.1            | 71.2                      | 160.0                               | 231.2                   |

| 1.2            | 77.4                      | 174.5                               | 252.0                   |

| 1.3            | 83.7                      | 189.1                               | 272.8                   |

| 1.4            | 90.0                      | 203.6                               | 293.6                   |

| 1.5            | 96.3                      | 218.2                               | 314.5                   |

| 1.6            | 102.6                     | 232.7                               | 335.4                   |

| 1.7            | 109.0                     | 247.3                               | 356.2                   |

| 1.8            | 115.3                     | 261.8                               | 377.1                   |

| 1.9            | 121.6                     | 276.3                               | 398.0                   |

| 2              | 128.0                     | 290.9                               | 418.8                   |

Reciever required to capture retrorelfected beam vs communication range for various misalignment angles includes CCR beam divergence of 0.5mrad (100 arc second) for 12.7 mm CCR

Figure 2-7: Receiver size required vs communication range at different misalignment angles

As seen in Table 2-1, when the CCR mirrors are misaligned by 30 arc-seconds, a 210 mm diameter collecting lens is required to capture the retroreflected signal. We see in Figure 2-7 how having 0 – 50 arc second misalignment of mirrors effected the beam spot deviation for a 12.7 mm CCR, if we have 50 arc-second misalignment on the mirrors, then the required collecting lens on the receiver end needs to be more than 600 mm in diameter for a 2 km optical communication range. The benchtop initial design and improvement of the receiver unit is discussed in Chapter 5.

## 2.4 Requirements of the MEMS Chip

We selected a BK7 (n=1.51 for 635 nm) [43] 12.7 mm, uncoated, TIR-based commercial CCR. The CCR has a 12.7 mm long front face where the light comes in, and three orthogonal sides on which the beam totally internally reflects before finally emerging from the front face parallel to the incident beam. As seen in Figure 2-8, all three orthogonal sides measure 7.77 mm from the vertex to the top of the side, and the two ends of the flat sides are connected by an arc

as shown in Figure 2-8. This meant that there was an approximate 7.77 x 7.77 mm active area on the CCR where we wanted our MEMS structures to interact with the evanescent waves during TIR. Dimensionally, we wanted a silicon on insulator (SOI) chip larger than 7.77 mm on one side to enable access to the electrostatic electrodes. We decided the dimension of the MEMS die would be 10 x 8 mm, which would give us an additional 2 mm area to place the electrode bond pads.

Figure 2-8: 3D model of the CCR illustrating the height and other dimensions [12]

We would like to use as little power as feasible to actuate the MEMS structures and meet the electrical requirements for the MEMS chip. We decide to use ½ AA (3.V) battery to power the transmitter unit, so we wanted to ensure that we can actuate the MEMS structures in 3-15 V range, using battery or commonly available compact DC-DC converters. The ability to move the MEMS structure in and out of plane would allow us higher contrast modulation, which meant that we wanted to have three electrodes and move the structure either in or out of plane. Additionally, a structure modulation frequency of ~ 1-10 kHz was desirable for high data rate, running them higher than that using the same actuation voltage will be worthwhile. In the next section we perform pull-in calculations for different styles of MEMS structures using this

information, and then compute the energy consumption per bit for our transmitter and compare it to existing, solely MEMS mirror-based CCR systems.

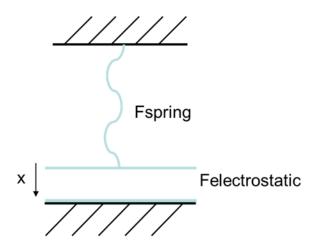

#### 2.4.1 MEMS Electrostatic Structures

There are several actuation methods available. For our application we needed an actuation method that had low power consumption, operated at a moderate-high frequency, was inexpensive to fabricate, and was unaffected during the bonding of the glass lid. We examined electrostatic, thermal, piezoelectric, magnetic, and other actuation methods, and determined that electrostatic actuation methods seemed to meet all the above criteria [44-46]. This, combined with our previous experience fabricating structures that use electrostatic actuation and limited resources and budget, led us to choose the electrostatic modulation method to actuate our structures. This concept is shown in Figure 2-9, in this method a mechanical spring is connected to one of the parallel plates. When potential is applied, the moveable parallel plate has electrostatic force that opposes the restoring force of the spring and moves towards the other plate.

Figure 2-9: An electrostatic actuator schematic with a spring connected to one of the parallel plates of capacitor. When pulled in, enough electrostatic force generated to overcome the spring's restoring force.

The force required to pull n springs by x distance is given by Equation 2.10, where k is the spring constant. The distance x is determined by the gap (also referred as sacrificial gap) between the parallel plate. If the sacrificial gap is g then the pull-in gap required (x) is one third the gap [35, 45, 47], as shown by Equation 2.11.

$$F_{spring} = nkx (2.10)$$

$$x = g/3 \tag{2.11}$$

Assuming that the springs are directly connected to the parallel plate in a straight line (also referred as straight tether format), the value of the spring constant k is given by Equation 2.12 [45, 47]. To improve accuracy, a detailed finite element analysis (FEA) of the spring needs to be performed. Equation 2.12 also uses the variables  $E_{silicon}$  (the Young's modulus of silicon), and w, t, and t (the width, thickness and length of the spring); we have added suffixes to each of these so that we do not confuse the spring and parallel plate variables.

$$k = E_{Silicon} w_{spring} t_{spring}^3 / l_{spring}^3$$

(2.12)

The counter-electrostatic force is given by Equation 2.13 [electrostatic], where  $\varepsilon_o$  is the permittivity of free space,  $l_{plate}$  and  $w_{plate}$  are the length and width of the parallel plate, V is voltage applied, and d is the gap between the parallel plates.

$$F_{electrostatic} = \frac{\varepsilon_o l_{plate} w_{plate} V^2}{2d^2}$$

(2.13)

When the parallel plates are pulled in, the spring is elongated by one third, and the parallel plate gap is two thirds its original gap with no voltage applied, so from Equations 2.10, 2.12, and 2.13, we get the pull-in voltage shown by Equation 2.14 [37, 44, 46]

$$V_{Pull-in} = \sqrt{\frac{8 n E_{Silicon} w_{spring} t_{spring}^3 g^3}{27 \varepsilon_o l_{plate} w_{plate} l_{spring}^3}}$$

(2.14)

We used Equation 2.14 to guide our design calculate the pull-in voltage for the different variants we intended to include in our mask design. We started with a 100 x 100 µm plate design and a spring with a width of 6 µm, a thickness of 3 µm, and length of 200 µm. Using four of these springs and a sacrificial gap of 3 µm, we got a pull-in voltage of 18.6 V. Similarly configured 200 x 200 µm and 500 x 500 µm plates gave reduced pull-in voltages of 9.3 V and 3.72 V respectively. We did not want to change a lot of variables, so, keeping the spring thickness (3 µm), gap (3 µm) and width (6 µm) constant, we altered the plate size, spring length, and number of springs to get structures with a wide range of pull-in voltages (Table 2-2). We used three different spring styles: short spring, long spring, and meander spring. All springs 200 µm and longer were of the meander type. It is important to note that these pull-in voltages illustrated in Table 2-2 are in plane, i.e. structure silicon moving towards the substrate silicon, however the gap between the glass and the MEMS structure will be in nm-range from Equation 2.14 and the pull-in voltage will be expected lower than this.

Along with the pull in voltages we also calculated the resonance frequency of the MEMS devices using Equation 2.15 [45]. The resonance frequency data will guide us as to what the optical communication data rates will be. The value of spring constant of an individual spring (k) was already available from Equation 2.12, to calculate the effective or complete spring constant we take the product of number of springs (n) and the spring constant of individual spring. To calculate the mass (m) of the plate, we calculated the area of MEMS plate and subtracted the area of release holes. The resonance frequency for each plate is also tabulated in Table 2-2 along with pull in voltages.

$$f_o = \frac{1}{2\pi} \sqrt{\frac{k_{total}}{m_{plate}}} \tag{2.15}$$

Table 2-2: Variation of MEMS structures along with their calculated pull-in voltages and resonance frequency

| Plate size ( in | Spring length | Number of | Calculated pull in | Resonance          |

|-----------------|---------------|-----------|--------------------|--------------------|

| μm)             | (in µm)       | springs   | voltage (in V)     | frequency (in kHz) |

| 100x100         | 200           | 4         | 10.14              | 7.12               |

| 200x200         | 55            | 4         | 35.18              | 24.69              |

| 200x200         | 150           | 4         | 7.81               | 5.48               |

| 200x200         | 200           | 4         | 5.07               | 3.56               |

| 500x500         | 450           | 4         | 0.6                | 0.42               |

| 500x500         | 250           | 4         | 1.45               | 1.02               |

| 500x500         | 150           | 4         | 3.12               | 2.19               |

| 500x500         | 150           | 8         | 4.42               | 3.1                |

Also important to note that in these calculations, bending and tipping effects are not considered, and the spring constant is an approximation, FEA analysis would yield more accurate information. However, these empirical calculations give us guidelines as how one parameter impact the pull-in voltage and resonance frequency, though the exact numbers may be off, however the trend that it shows is accurate. We used the information form these calculations and designed and fabricated the structure that will be discussed in detail in the next chapter.

## 2.4.2 Calculation of Energy Needed Per Bit

In this section we calculate the energy consumed per bit using our suggested communication method, which will enable us to compare this model with other communication methods and to understand its key merits. In the above designs, the parallel plate moves in and out of plane as each bit is being transmitted. This means we can calculate the energy required per bit by first computing the capacitance of the parallel plate as given by Equation 2.16 [37, 45] and